Samsung запускає 3D-пакування чипів – нові процесори дозволять розміщувати ШІ на смартфонах

Чипи для автономного ШІ на крок ближче

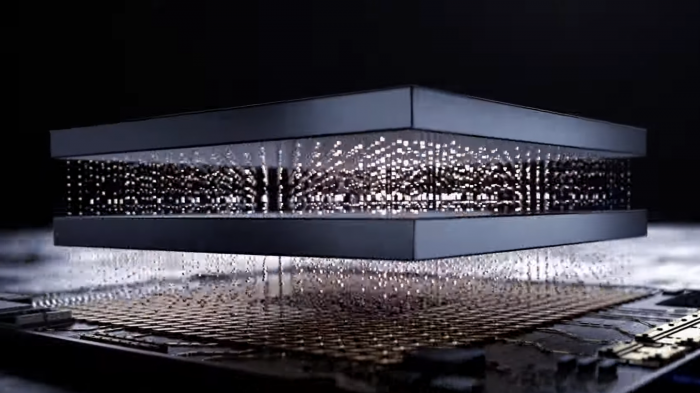

Samsung Electronics готова запустити процес 3D-пакування чипів у 2024 році. Цей інноваційний підхід передбачає вертикальне розміщення різнорідних напівпровідників, що є ознаменуванням нової ери високопродуктивних мікросхем штучного інтелекту з низьким енергоспоживанням.

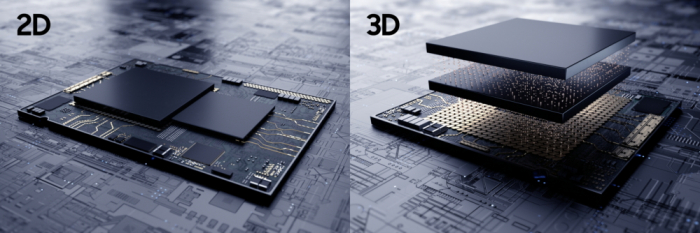

На відміну від традиційного горизонтального розміщення чипів, 3D-пакування передбачає укладання транзисторів вертикально. Ця конфігурація сприяє швидшій обробці даних між напівпровідниками та значно підвищує енергоефективність. необхідність функціонування ШІ вимагає якомога більш енергозаощаджувальних технологій, і просторове пакування стало у пригоді.

Рушійною силою цієї ініціативи є використання передової технології SAINT (передова технологія взаємозв’язку Samsung). Цей інноваційний процес передбачає з’єднання різних типів чіпів для злагодженої роботи як єдиного блоку. На відміну від звичайного горизонтального розміщення, 3D-упаковка відрізняється вертикальним розміщенням мікросхем.

Компанія Samsung Electronics успішно завершила технічну перевірку SAINT(Samsung Advanced Interconnection Technology). Вона полягає в укладанні SRAM, яка служить тимчасовим сховищем даних, поверх процесора. Samsung планує завершити перевірку технології SAINT-D у наступному році. SAINT-D передбачає розміщення DRAM для зберігання даних поверх CPU та GPU. У розробці знаходиться SAINT-L, призначена для розміщення додаткових співпроцесорів.

Новий процес виробництва зокрема застосовуватиметься для створення чипів, яки здатні запускати моделі ШІ на окремому пристрої. Конкуренти Samsung також не стоять на місці. TSMC, UMC і Intel також змагаються за розробку передових технологій пакування. TSMC пропонує послугу 3D-пакування SoIC, яка обслуговує таких великих гравців, як Apple та NVIDIA. Intel використовує Foveros, власну технологію 3D-пакування, для масового виробництва.

Джерела: Sparrows News, Samsung